- Home

- 受託試験サービス

- デバイス/モジュールの信頼性評価、電気的特性測定・評価

- 信頼性評価

- WLR(Wafer Level Reliability)評価

デバイス/モジュールの信頼性評価、電気的特性測定・評価

WLR評価: 高信頼性プロセスの確立と製品の高信頼性確保のため、WLR評価サービスを提供

WLR(Wafer Level Reliability)評価

TEGを用いた信頼性評価手法

製品のように複雑な集積回路の評価では、特にプロセスに起因する信頼性の問題点を絞り込むことが非常に困難なため、TEGを用いた信頼性評価が有効です。製品段階で発生する可能性がある信頼性の問題は、できるだけ早期に検出し、設計、プロセスにフィードバックすることが重要です。OKIエンジニアリングでは、高信頼性プロセスの確立と製品の高信頼性確保のため、WLR(Wafer Level Reliability)評価サービスを提供しています。

WLR(Wafer Level Reliability)評価とは

ウエハレベルで、効果的に信頼性を評価する手法です。TEGウエハのゲート酸化膜の各種パラメータ(TZDB、TDDB、ホットキャリア等)の測定サービスをご提供いたします。

![]()

特徴

特徴は、あらかじめ想定した故障メカニズムごとに製作したTEGを、専用の測定プログラムにより評価を行う点です。

- 専用のプログラムにより効果的に大量データの取得が可能

- ウエハーレベル加速試験の実施により評価時間の短縮が可能

- ウエハーレベルでプロセス要素の信頼性評価が可能

- -45℃~+150℃の温度特性が可能(例:ホットキャリア(HCI)、NBTI等)

- マトリクス・スイッチにより多数個同時測定が可能。

用途

- プロセス開発段階→高信頼性プロセスの早期立ち上げをサポートするTEG(例)

- 製品やTEGの信頼性試験に先行したプロセス信頼性評価

- プロセス開発過程での信頼性の安定性、ばらつき評価

- プロセス選択時の相対評価、確認評価

- 生産段階→生産工程における信頼性モニターTEG(例)

- 信頼性問題の未然検出

- 生産工程でのプロセス信頼性の安全性モニタ

- 生産プロセスの工程変更可否判断評価

ダメージTEGウェハのゲート酸化膜の評価事例

下記の図は前工程で使用されるプラズマ装置の開発におけるダメージTEGウエハのゲート酸化膜の評価事例です。(1)未処理品、(2)プラズマ処理A、(3)プラズマ処理BのTZDB(Time Zero Dielectric Breakdown :瞬時絶縁破壊)、TDDB(Time Dependent Dielectric Breakdown :経時絶縁破壊)の評価事例をご紹介します。TZDB評価でプラズマ処理Bはゲート酸化膜へのダメージが大きいことがわかります。さらに、TDDB評価では、TZDBで差が観測されなかった未処理品とプラズマ処理Aの差異が観測されます。

![]()

- TZDB評価条件:ゲート酸化膜(4µm²)に0~10Vまで、0.2Vステップで電圧印加時のリーク電流測定(判定:1uA)

- TDDB評価条件:ゲート酸化膜(4µm²)に定電流(10nA)ストレスを印加して、破壊するまでの時間を測定

ウエハご提供:株式会社フィルテック殿

TDDBとは

TDDBはTime Dependent Dielectric Breakdown(経時的絶縁破壊)の略であることからも分かるように、絶縁耐圧以下の電圧でも、印加しつづけることによって経時的に絶縁破壊にいたる現象をいいます。主にMOSトランジスタのゲート酸化膜が対象となっています。TDDB劣化の発生メカニズムとして、Percolationモデルでは酸化膜に印加された電圧や酸化膜中の電流によって生じた酸化膜中の欠陥が経時的に増加し、欠陥間の距離が近くなることで電子の移動が活発化、酸化膜中に電流パスが発生して絶縁破壊に至ると考えられています。近年、トランジスタの微細化に伴うゲート酸化膜の薄膜化と電界強度の増加のためTDDBは半導体における重要な不具合要因の一つとなっています。このように、ある電界を印加したとき、酸化膜が破壊に至るまでの時間をTDDB寿命といい、絶縁破壊の時間依存性をはかる尺度と考えられています。TDDB寿命測定には定電圧ストレス法と定電流ストレス法があります。

ゲート酸化膜の寿命測定(TDDB測定)

当社では、これまでに、ウエハの面内分布を見る目的で、TDDB測定を取り入れウエハの評価を実施しています。また、ゲート酸化膜の寿命測定としては、たとえば下記のようなTDDB測定を実施することで求められます。

- 印加電圧条件3水準

- 周囲温度条件3水準

各条件でのTDDB測定結果をワイブルプロットし、平均寿命を計算します。 その結果を元に活性化エネルギーを算出し、実使用での寿命を算出することができます。

![]()

TDDB測定データのワイブル表記

MOSFETの特性評価事例

評価用TEGウエハを用いて、MOSFETの基本特性を取得し、低温環境におけるホットキャリア評価、高温環境におけるNBTI評価を実施しました。

- 使用装置

- 特性取得装置:半導体パラメータアナライザー B1500A(アジレントテクノロジー製)

- 構成

- HR_SMU 4台、HP_SMU 1台、CMU 1台

- プローバ

- オートプローバ Precio XL(東京エレクトロン製)

温度範囲:-45℃~150℃

針対応:マニピュレータ使用による4本コンタクト

プローブカード使用による多数個コンタクト

E5255A内蔵のマトリクススイッチE5250A(アジレントテクノロジー製)により8個同時評価可能

基本特性取得

3.3V-PMOS/NMOSに対して基本特性を取得しました。

ホットキャリア(HCI)評価事例

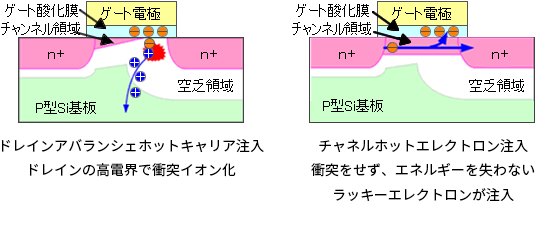

ホットキャリア:HC(Hot Carrier)現象とは?

ホットキャリアによる素子劣化は、チャネルのキャリア(電子または正孔)が、高電界領域で電界加速により大きなエネルギーを得ることで引き起こされる現象です。大きなエネルギーを得た電子は、電位障壁を乗り越えゲート酸化膜中に注入され、トラップされます。その結果、MOSFET のしきい値電圧(Vth)および伝達コンダクタンス(gm)などの特性が劣化します。ホットキャリア劣化を加速する要因には電源電圧、チャネル長、保護膜中の水素、温度などがあります。

評価事例

評価TEG用のNMOSトランジスタを-40℃環境にて、Vgs=1.6V、Vds=4.4V印加による評価を7000秒まで実施しました。その結果、10%劣化時間は77800秒となりました。

NBTI評価事例

NBTI(Negative Bias Temperature Instability)現象とは?

NBTIとは、トランジスタのゲート電極に対して基板の電位が負の状態でチップの温度が高まるとp型トランジスタのしきい値電圧の絶対値が次第に大きくなっていく現象です。ゲート・ボディ間にバイアスが印加されると、エネルギーの高いホットホールが発生し、そのホールがゲート酸化膜に注入され、素子の劣化を引き起こします。

評価事例

評価TEG用のPMOSトランジスタを125℃環境にて、Vds=-4.4V印加による評価を7000秒まで実施しました。その結果、10%劣化時間は3030秒となりました。

ダイナミックリカバリの影響の回避

NBTIでは、Ionモニターの時に、ゲートに印加していたストレス電圧をoffし、代わりに測定用電圧を印加しますが、その際、ダイナミックリカバリによりIon劣化が小さく見えることがあります。このため、Ion測定をストレス電圧offから0.1msec後に行い、ダイナミックリカバリの影響を回避しています。

- デバイス/モジュールの信頼性評価、電気的特性測定・評価のお問い合わせ先

- WEBからのお問い合わせ:お問い合わせフォームはこちら

電話:03-5920-2366