デバイス/モジュールの信頼性評価、電気的特性測定・評価

バーンイン試験

バーンイン試験とは、温度と電圧の負荷をかけることにより、初期不良を事前に低減させる方法であり、自動車、宇宙防衛、社会インフラ系の企業をはじめとし、多くの企業が用いるスクリーニング試験のなかでも初期不良検出に最も有効な試験の一つです。

バーンインには、試験中に電気的な動作をさせるダイナミックバーンインと電圧印加のみのスタティックバーンインがあり、両者対応が可能です。特にダイナミックバーンインは、高温環境下でデバイスを動作させるため、市場での使用状態に近づけたスクリーニング試験が実施できます。また、昨今、市場流通品を使用した製品でのトラブルが多発しており、特性変動の事前把握にも効果が期待されます。OKIエンジニアリングでは入出力条件が異なるFPGA、ASIC、アナログ混載SoC、高速動作デバイス等について、様々な試験条件に対応したバーンイン試験サービスを提供します。

バーンインの効果

- 安定した品質のデバイスを供給

- ユーザー満足度の高い品質を保持

- 不良デバイスの市場流出を抑止

- 初期不良品の除去

-

市場流通品を使用する場合の特性変動の把握

対応可能品種

- 汎用ロジックICからASIC、アナログ混載SoC

- メモリ(SRAM、PROM、EEPROM等)

- FPGA等のプログラマブルデバイス(FPGA、EPROM、EEPROM、RTAX2000、RTSX32、RTSX72、RH1280等)

初期不良品の除去

電気的特性試験

ダイナミックバーイン試験による市場流通品の特性変動事例

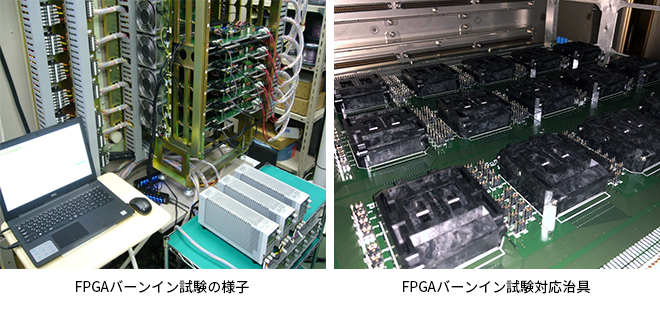

FPGAのバーンイン試験事例

特にFPGA等は端子の設定によっては入出力条件が変わることで、バーンインボードの再製作が必要になる等、初期コストの増大が問題化してます。このような悩みにお応えするため、比較的低コストで大容量のテストパターンに対応可能なダイナミックバーンイン試験をご提供します。

| テストパターンステップ数 | 最大10Mステップ(信号の変化点を1ステップ) |

|---|---|

| テストパターンフォーマット | 一般的な論理記号("1","0")の他、VCDフォーマット、WGL,STILに対応可能 |

| テストパターン数 | 最大5テストパターンを並行して試験可能 |

| 最大信号数 | 256信号線 |

| 電源系統 | 標準仕様 2系統(オプション:2系統以上にも対応可能) |

| 電源電圧 | 標準仕様 VccCore(2.25V~6.00V),VccIO(3.00V~6.00V) |

| 入力電圧 | 標準仕様 VIH(2.00V~5.5V),VIL(0.4V以下) |

標準仕様の他、個別対応も可能です。

アナログ混載デバイスのバーンイン試験事例1

画像処理ASIC(※1)のNTSC(※2) I/Fに実動作に近いNTSC信号を入力して、ダイナミック・バーンイン試験を実施した事例です。

- 対象デバイス

- 画像処理ASIC

- ロジック部テスト周波数

- 1MHz

- アナログ入力部

- NTSC信号

- テストパターン長

- 1Mステップ未満

アナログ混載デバイスのバーンイン試験事例2

電源監視ICのアナログ入力部に負荷を印加する為、任意波形を入力してダイナミック・バーンイン試験を実施した事例です。

- 対象デバイス

- 電源監視IC

- ロジック部テスト周波数

- 1MHz

- アナログ入力部

- 任意波形(0~1V周期変化)

- テストパターン長

- 1Mステップ未満

高速動作対応のバーンイン試験事例

ASICの実動作に近い高速クロック(66MHz)を入力して、ダイナミック・バーンイン試験を実施した事例です。(発振器は高温で動作できる部品をスクリーニングし選定)

- 対象デバイス

- 66MHz動作ASIC

- ロジック部テスト周波数

- 66MHz

- テストパターン長

- 1Mステップ未満

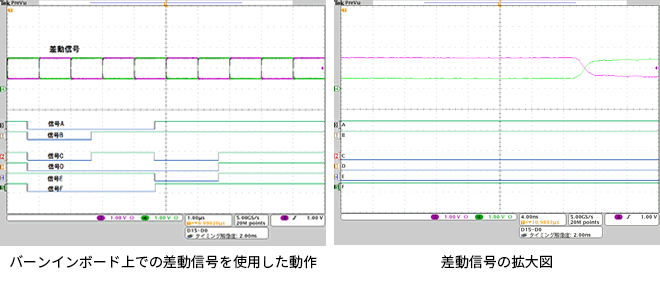

差動信号入力デバイスのバーンイン試験事例

差動信号入力が要求されるダイナミックバーンインにおいて、差動信号のクロスポイントが重要になります。要求信号は市販のLVDSデバイスの出力信号では対応できない信号幅の場合もあり、この場合、LSIテスター規模の発生信号が必要になります。CTS社製LSIテスターを使用し、要求される差動信号に対応したダイナミックバーンイン試験を実施した事例です。

基本構成

![]()

ダイナミックバーンインシステムでLSIテスターを使用するメリット

高い波形品質(信号間のスキュー、slew rate、etc)、高速動作で実力を発揮します。安定した差動信号での動作を実現できます。

OKIエンジニアリングでは、CTS社製LSIテスターを使用し、より高度なダイナミックバーンイン試験のサービスをご提供いたします。

- ※1 ASIC:Application Specific Integrated Circuit 特定の用途・顧客向けに設計した集積回路

- ※2 NTSC:National Television System Committee 「全米テレビジョン放送方式標準化委員会」の略称で、同委員会が策定した映像信号とテレビ放送の方式名称として使用される

- デバイス/モジュールの信頼性評価、電気的特性測定・評価のお問い合わせ先

- WEBからのお問い合わせ:お問い合わせフォームはこちら

電話:03-5920-2366