- Home

- 受託試験サービス

- ESD試験・TLP測定

- ESD/ラッチアップ(Latch-up)実力・解析試験

ESD試験・TLP測定

ESD/ラッチアップ(Latch-up)実力・解析試験: LSIのESD耐量とラッチアップ耐量をデバイス開発段階で実力値まで確認し、故障発生時の解析から確実な改良対策案までをご提供

ESD/ラッチアップ(Latch-up)実力・解析試験

LSIのESD耐量とラッチアップ耐量をデバイス開発段階で実力値まで確認し、故障発生時の解析から確実な改良対策案までをご提供します。ESDやラッチアップ試験は、量産に関わる重要な信頼性試験です。ESDやラッチアップの不良が発生すると、解析から対策案創出、試作期間の確保のため、量産時期の見直しが発生します。さらに、解析、マスク改修や試作などの追加費用も必要となります。そこで、デバイス開発段階での実力値把握と懸案点の洗い出しが重要となり、この確認と対策により量産までのTAT短縮が図れ、量産後の安定した性能確保が実現できます。

ESD/ラッチアップ(Latch-up)実力・解析試験のメリット

- メリット1

ESD、Latch-up実力試験では、改善が必要な端子はもとより、過剰に耐量マージンのある端子が判明しますので、開発段階でのESDおよびLatch-up対策最適化が可能となります。 - メリット2

ESD、Latch-up実力試験後の測定評価は、当社所有のテスターを使用すれば実力試験の時間短縮が可能となります。テストプログラムの作成・変換や測定ボードおよびプローブカードの設計・作成も承っています。 - メリット3

ESD、Latch-up実力試験後にデバイスの問題を発見した場合は、その解析から改良のご提案まで総合的な試験サービスをご提供いたします。

ESD/ラッチアップ(Latch-up)実力・解析試験の流れ

問題点抽出:故障が発生した場合、その不良程度の見極めを行い問題点を抽出します。

損傷箇所解析:解析装置、分析装置を使用して損傷箇所の特定と解析を行います。

損傷メカニズム解析:特性評価や損傷箇所解析から、損傷メカニズムを推定します。

改良提案:故障原因の特定とメカニズム解析の説明を行い、改良のご提案をいたします。

設備一覧

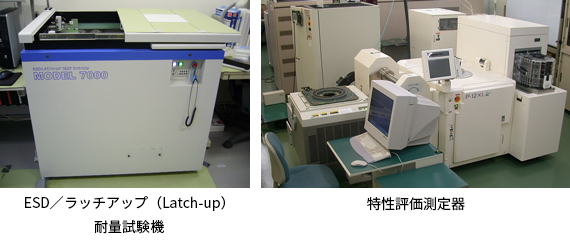

ESD/ラッチアップ(Latch-up)耐量試験機

特性評価測定器

- ESD試験・TLP測定のお問い合わせ先

- WEBからのお問い合わせ:お問い合わせフォームはこちら

電話:03-5920-2366