- Home

- 受託試験サービス

- ESD試験・TLP測定

- TLP測定(Transmission Line Pulse)

ESD試験・TLP測定

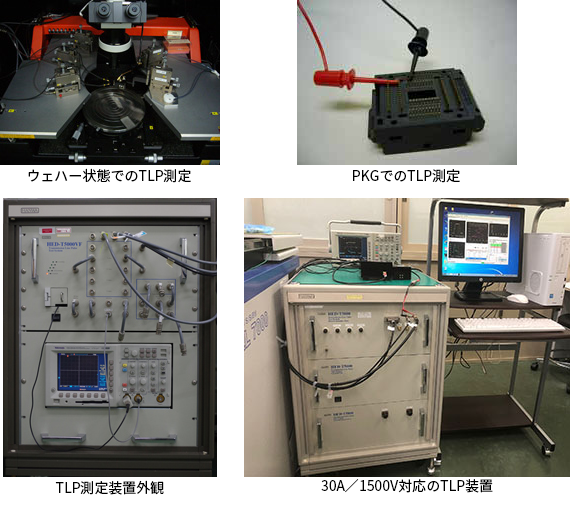

TLP測定: OKIエンジニアリングでは、TDR、TLP測定手法を用いることにより、精度の良いESD-Event時の特性およびESDパラメーターをご提供いたします。

TLP測定(Transmission Line Pulse)

TLP(Transmission Line Pulse)測定とは、パルスをトランジスターや集積回路に印加し、ESD保護素子やESD保護回路の電圧(V)/電流(I)特性のデータを取得することです。集積回路のESD保護設計において、保護素子や保護される素子がESDサージのような時定数の短いパルス波に対して、どのようなI-V特性で、どのくらいの電流まで許容できるかを把握しておくことは非常に重要です。通常のDC測定では熱破壊を招いてしまう場合も、TLP装置による測定は熱破壊を起こしにくく、大電流領域(~10A)の特性を確認・取得することができます。さらに、TLP測定を実際の集積回路に用いることにより、ESD保護設計だけではなく、ESD起因で発生する不具合に対する解析ツールとしても活用できます。また、OKIエンジニアリングでは、30A/1500V対応のTLP装置を新規に導入し、半導体ウェハーやベアチップへだけでなく、パッケージ組立品や基板モジュール、さらには、実装基板の保護回路設計を支援できる体制を整えました。OKIエンジニアリングでは、TDR(Time-Domain- Reflection)TLP測定手法を用いることにより、精度の良いESD-Event時の特性およびESDパラメーターをご提供いたします。

TLP測定サービス概要

実装基板のTLP測定の様子

- TLP測定による保護素子および被保護素子等のESD-Event時の動作特性が取得可能

- TLP測定による各素子の精度の良いESDパラメーター抽出が可能

- 測定素子は、ウェハー状態、チップ状態、パッケージ組立品や基板モジュールまで幅広く対応可能

- TLP測定により抽出したESDパラメーターを用いて、ESD保護設計への応用活用が可能

- LSIへのTLP測定により、ESD起因で発生する不具合に対する解析ツールとしての活用が可能

- ESD保護素子・ESD保護回路の最適配置設計アドバイスが可能

- 最大電流30V、最大電圧1500Vの測定が可能

TDR(Time-Domain- Reflection)-TLP測定原理

TDR-TLP測定法は、測定素子(DUT)に矩形波を印加し、その時のDUTからの反射波をオシロスコープで観測し解析することにより、素子のESD-Event時の動作特性を得る方法です。

TLP測定装置構成概要

測定素子(DUT)に印加する矩形波は、パルス発生部の同軸ケーブルに電荷を蓄え、DUT側の伝送経路に切り替えることにより形成します。その矩形波は、フィルターを介して波形の立ち上がりを制御した後、伝送経路を通してDUT側へ印加されます。このときの、入射波の電圧・電流波形は、「DUT-パルス発生部」間の波形観測部にあるオシロスコープで観測します。DUT部と伝送線路のインピーダンスミスマッチングが発生している場合、DUT部で消費し切れなかったエネルギーが反射波として、波形観測部を通過します。波形観測部では、入射波と反射波が合成されてオシロスコープで観測されますが、合成された部分が、DUTの過渡現象として観測されます。この合成された部分の波形を平均化した値をI/V曲線としてプロットし、その曲線を素子のESD-Event動作特性として抽出します。

TLP測定結果例

Nch MOS-FET ESD保護素子のTLP測定例

ゲートをOFFに固定したESD保護として使用するNch MOS-FETのI-V特性をTLPで測定しました。塗りつぶしのプロットがI-V特性、白抜きのプロットがリーク電流になります。ゲート幅(W)が大きくなるにつれ破壊電流(白抜きプロットが右に移動するとリーク大=破壊)が大きくなることが確認できます。さらにターンオン電圧(ブレークダウンからスナップバックに入る電圧)、ON抵抗(スナップバック後の傾き)でもゲート幅(W)によって違いがあることが確認できます。

Nch MOS-FETのI-V特性(ゲート依存)

Nch MOS-FET ブレークダウン電圧のTLP測定例

Nch-MOS-FETにおいてゲート電圧を印加しない状態(VGS=0V)と印加した状態(VGS=1~3V)のブレークダウン電圧をTLPで比較しました。チャネルをONさせると、ブレークダウン電圧が低下することが確認できます。この特性はESD保護素子に用いられる場合があります。

Nch MOS-FETのゲートバイアスによるブレークダウン特性比較

ダイオード ESD保護素子のTLP測定例

還流ダイオードに使用される耐圧600Vクラスのダイオードのブレークダウン後のI-V特性を、30V/1500V対応TLP装置で測定しました。675Vから電流が流れ始め、750V近辺で電導度変調を起こし、Vb=730V、Ib=11Aに達した時点で破壊したことを示しています。 (Vb:ブレークダウン電圧、Ib:ブレークダウン電流)

ダイオード(耐圧600V)のブレークダウン特性

- ESD試験・TLP測定のお問い合わせ先

- WEBからのお問い合わせ:お問い合わせフォームはこちら

電話:03-5920-2366