2020 OEGセミナー

# TLPを用いた実装基板の ESD保護回路設計サービス

~ESD Design Windowを活用した新たなESD保護設計~

2020年 11月 6日

沖エンジニアリング株式会社 デバイス評価事業部 市川 憲治

## 目次

- 1. ESD保護

- 2. システム・基板レベルのESD保護方法と問題点

- 3. 今回の目的

- 4. TLPとは

- 5. ESDデザインウィンドウ(TLPデータの活用例)

- 6. プリント基板へのTLP測定の応用例

- 7. まとめ

### 1. ESD保護

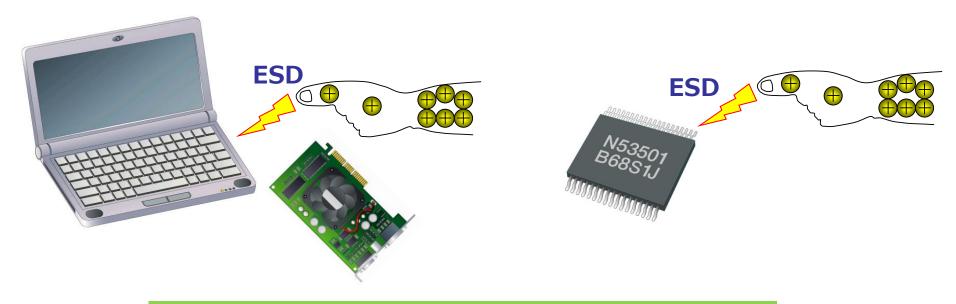

### **ESD** (Electro-Static Discharge)

直訳すると「静電気放電」。

蓄積された静電気電荷の放電のことを言うが、「静電気放電によって半導体デバイスが破壊される現象」として使われることが多い。

帯電物体や放電のメカニムズによりいくつかのモデルに分類されている。

半導体デバイス、電子機器が静電気で破壊されない ようにするためのESD保護素子が必要

### 2. システム・基板レベルのESD保護方法と問題点

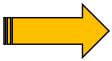

#### 【システム・基板レベルのESD保護方法】

実装基板の外部インターフェース接続端子などにTVS(Transient Voltage Suppressor) と呼ばれるツェナーダイオードなどのサージ保護部品を基板上に取り付ける

#### 【システム・基板レベルのESD保護の問題点】

- ▶ 保護される側の破壊電圧がわからないために取り付けるサージ保護部品の選択ミスが起こりやすい(破壊が起こるまでTVSが動作しないミスマッチも多い)

- ▶ TVSのデータシートでは応答電圧の記載はあるが、電流能力が読み取れないので 適切なサージ保護部品を選択したつもりでも破壊が起こることがある

ESD評価においてカット&トライの連続になりがち

### 3. 今回の目的

# それらの問題を解決するために・・・

- → 部品レベルのESD保護設計で培ってきたTLPによる最適保護 設計の手法を実装基板レベルに適用

- ➤ 国内初となるTLPを用いた実装基板のESD耐性改良ワンストップ プ評価サービスを立ち上げ

これらのサービス内容について紹介させていただきます

### 4. TLPとは

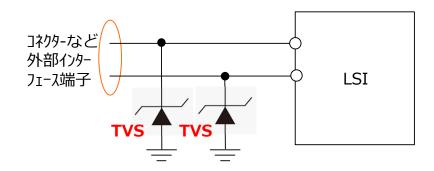

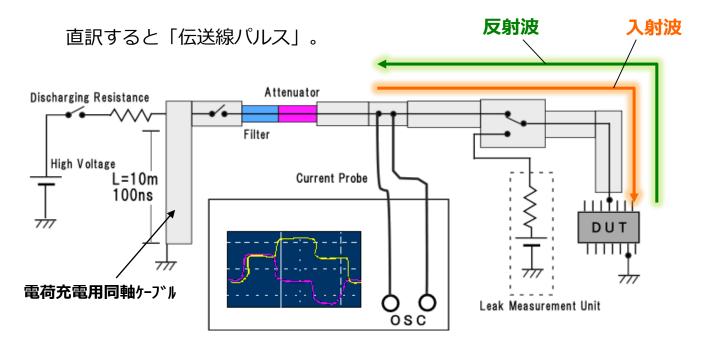

#### **TLP** (Transmission Line Pulse)

に近い100ns程度の パルスによる測定に なるので大電流領域の 測定が可能 電流 [A] DC測定は流れる電 流により熱破壊を 起こすので大電流 領域の測定が困難 電圧 [V]

TLP測定は静電気放電

高圧電源から同軸ケーブルに蓄えられた電荷を放出して得られる矩形波をDUTに印加、入射波とDUTからの反射波との合成波を解析することでESDイベントにおけるI-V特性を取得する手法。主に半導体デバイスの保護回路設計ツールとして使われる。

TLP測定は静電気放電に近い100nsec程度のパルスによる測定になるのでDC測定では熱的ストレスに厳しい大電流領域のI-V測定が可能になる

DUT: Device Under Test (検査対象機)

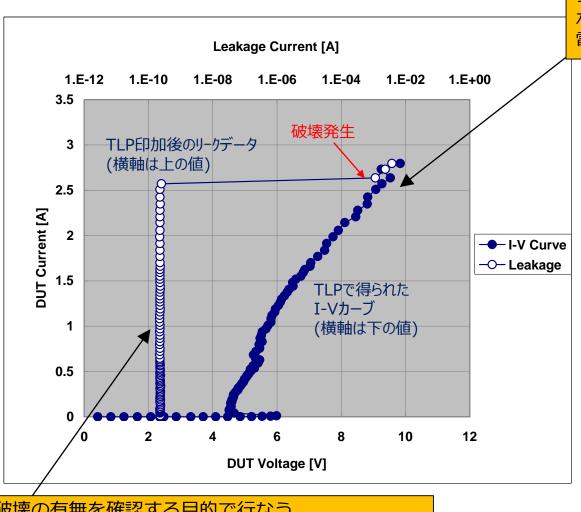

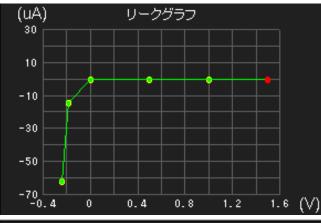

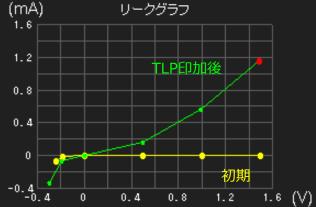

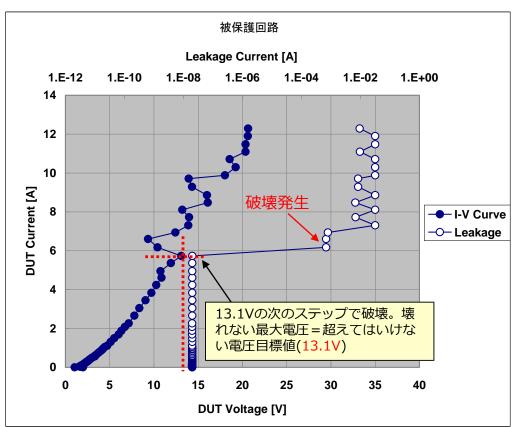

## TLPデータの見方

#### TLPデータ例

1つ1つのプロットがTLP印加電圧に対して オシロスコープで読み取ったデバイスに掛かる 電圧と電流のポイント(横軸は下の値)

DCリーク測定 (リーク無し)

破壊

DCリーク測定 (リーク有り)

破壊の有無を確認する目的で行なう 各TLP印加後のDCリーク測定値(横軸は上の値)

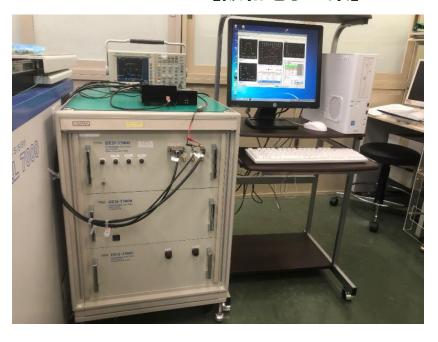

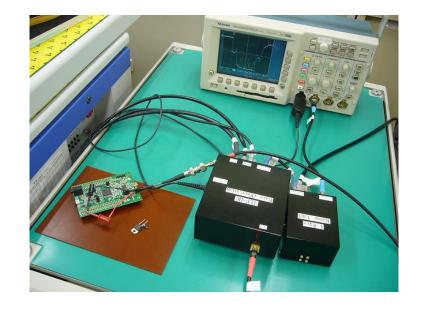

## TLP装置

#### 基板レベルのESD保護設計に使用する **HED-T5000-HC [阪和電子工業]**

部品レベルのESD保護設計に使用していた HED-T5000 [阪和電子工業]

|         | HED-T5000-HC              | HED-T5000                |

|---------|---------------------------|--------------------------|

| パルス幅    | 100nsec, 200nsec          | ←                        |

| パルス立上り  | 0.2ns, 2ns, 10ns, 20ns    | ←                        |

| TLP印加電圧 | 最大750V<br>(Open時は最大1500V) | 最大250V<br>(Open時は最大500V) |

| TLP電流   | 最大30A                     | 最大10A                    |

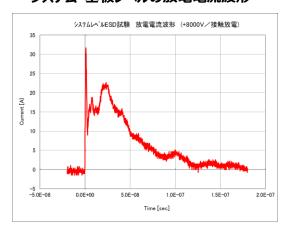

#### システム・基板レベルの放電電流波形

参照規格例: IEC61000-4-2

| N,\\ | 印加電圧 | t°-ク電流 |

|------|------|--------|

| 1    | 2kV  | 7.5A   |

| 2    | 4kV  | 15A    |

| 3    | 6kV  | 22.5A  |

| 4    | 8kV  | 30A    |

## 5. ESDデザインウィンドウ(TLPデータの活用例)

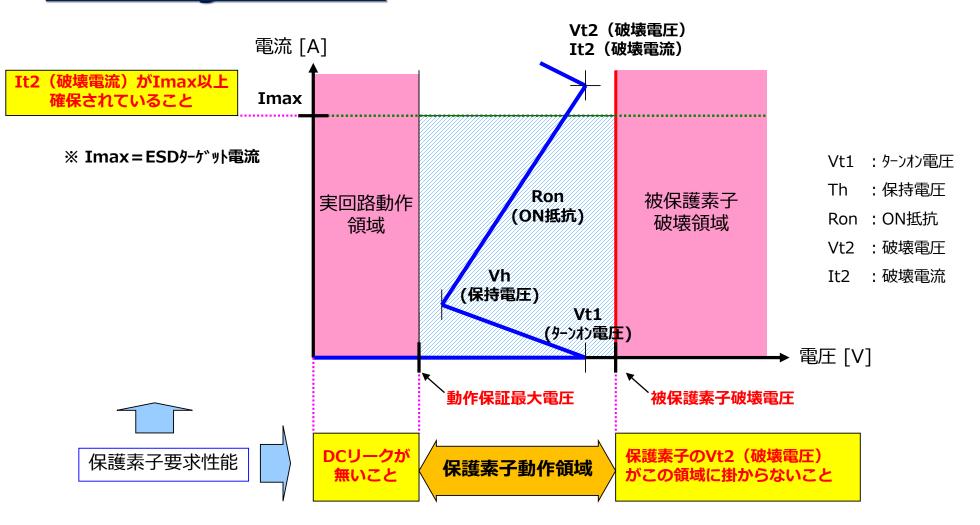

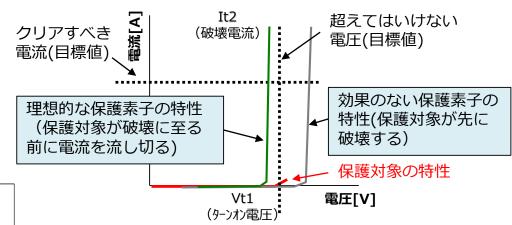

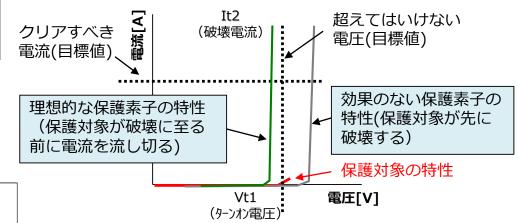

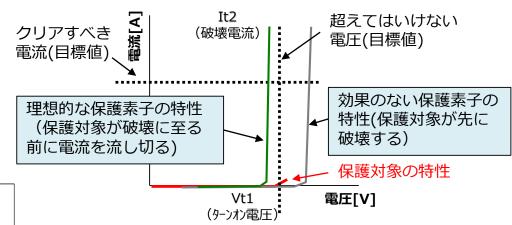

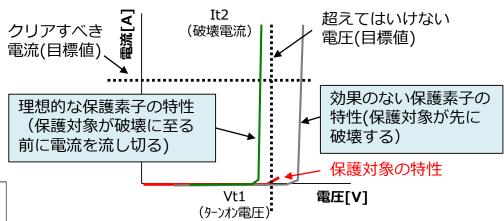

### **ESD Design Window** ~ ESD保護設計の考え方 ~

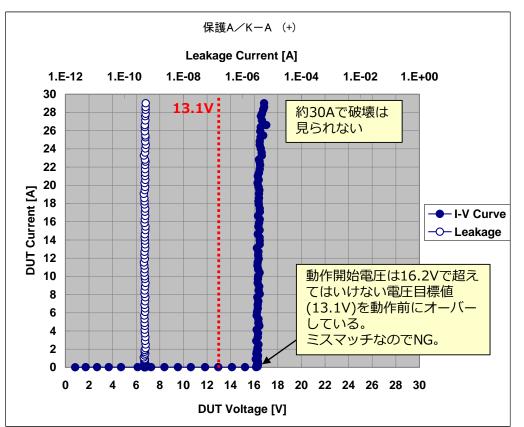

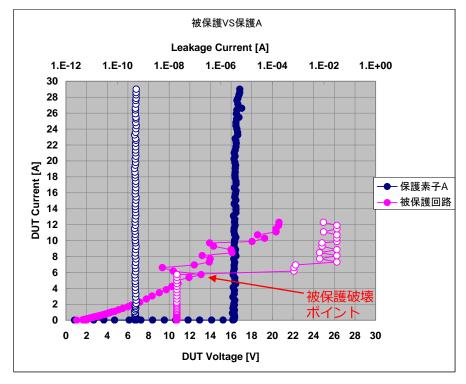

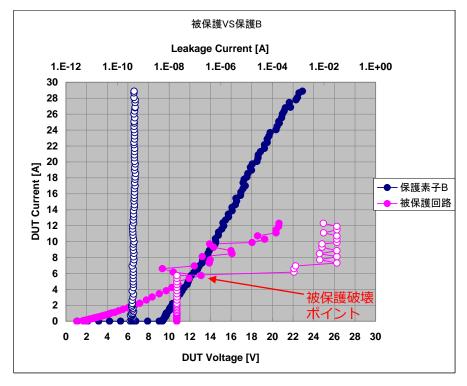

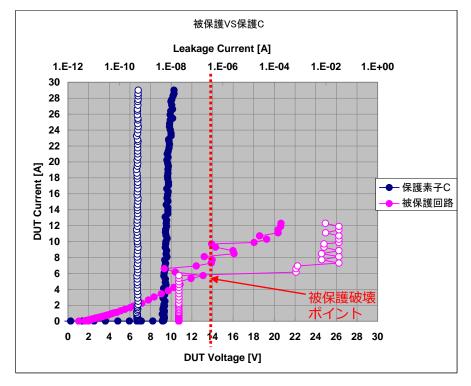

STEP1:保護される側のTLP特性調査 (マイコン基板の外部機器接続端子)

保護される側の回路が何Vまで耐えられるかを確認 ⇒ 13.1Vで破壊

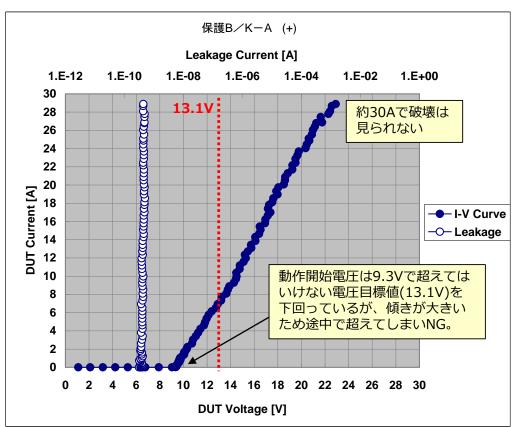

STEP 2: ESD保護部品のTLP特性調査 (ツェナーダイオード①/Vz=16V)

電流流れ初め電圧 = 16.2V → NG IEC61000-4-2接触放電レベル4 (30A) 相当を流し切るまでの上昇電圧 = 17V → NG

STEP 2: ESD保護部品のTLP特性調査 (ツェナーダイオード②/Vz=9V)

電流流れ初め電圧 = 9.3V → **OK** IEC61000-4-2接触放電レベル4 (30A) 相当を 流し切るまでの上昇電圧 = 23.8V → **NG**

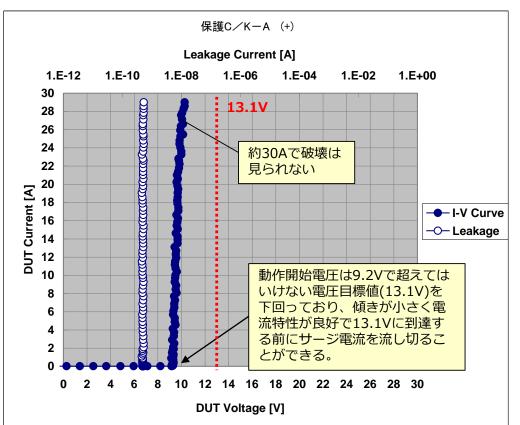

STEP 2: ESD保護部品のTLP特性調査 (ツェナーダイオード③/Vz=9V)

電流流れ初め電圧 = 9.2V  $\rightarrow$  **OK** IEC61000-4-2接触放電レベル4(30A)相当を流し切るまでの上昇電圧 = 10.3V  $\rightarrow$  **OK**

### TLP測定により適正なESD保護部品の選定ができたら・・・

#### STEP3: ESD保護部品を基板に実装してTLP特性を調査

・基板上での取付位置による特性変化量を把握(配線抵抗などが影響)

STEP4: ESD保護部品を実装した基板、または基板を組み込んだシステムでESD試験を実施、実力確認

・IEC61000-4-2準拠のESD試験規格を満たすことを確認

実装基板のESD耐性改良ワンストップ 評価サービスを提供いたします

### 7. まとめ

- → 部品レベルのESD保護設計で培ってきたTLPによる最適保護設計の 手法を実装基板レベルに適用

- ・最大30AのTLP装置を実装基板レベルの評価に適用することで、 IEC61000-4-2『静電気イミュニティ試験』の接触放電レベル4=±8kV までのESD保護設計が可能になった

- ・ESD Design Windowを活用したTLPデータの定量的な分析による 確実なESD保護で、カット&トライに費やしてきた時間と費用を削減可能 (部品選定のミスマッチによる手戻りを解消)

- ➤ 国内初となるTLPを用いた実装基板のESD耐性改良ワンストップ 評価サービスを立ち上げ

- ・実装基板上でのTLP評価からシステムレベルのESD試験まで最適な評価プランを提案し、ワンストップでのESD耐性改良に対応いたします

## ご清聴いただき、ありがとうございました