2016 OEGセミナー

# EMC設計の成功ポイント

2016年7月12日

沖エンジニアリング株式会社 EMC事業部 戸所祐策

## 目 次

- 1. EMC設計サービス

- 1.1 EMC設計の目的

- 1.2 EM規格クリアの為の重要ファクタ

- 2.工程毎レビューの有効性

- 2. 1 方式設計レビュー

- 2. 2 具体設計レビュー

- 2. 3 シミュレーションレビュー

- 2. 4 評価レビュー

- 3. 電源デバイスのEMCの留意事項

- 4. まとめ

EMC【 Electro-Magnetic Compatibility 】電磁両立性

# 1. OKIエンジニアリングのEMC設計サービス

OKIエンジニアリングでは、EMC規格をクリアするために、評価段階での切り分け・提案のみならず、設計段階からEMC設計にご協力いたします

#### 1.1 EMC設計の目的

◇ 品 質: EMC規格を満足する

◇ コスト:評価費用・対策部品コストを削減、再設計による設計コストを削減する

◇ 納 期 : 出荷スケジュールを確保し機会損失をふせぐ

# 1.2 EMC規格クリアの為の重要ファクタ

- ◆ ローカルレビュー実施 お客様の過去資産を有効活用するためレビューを実施する

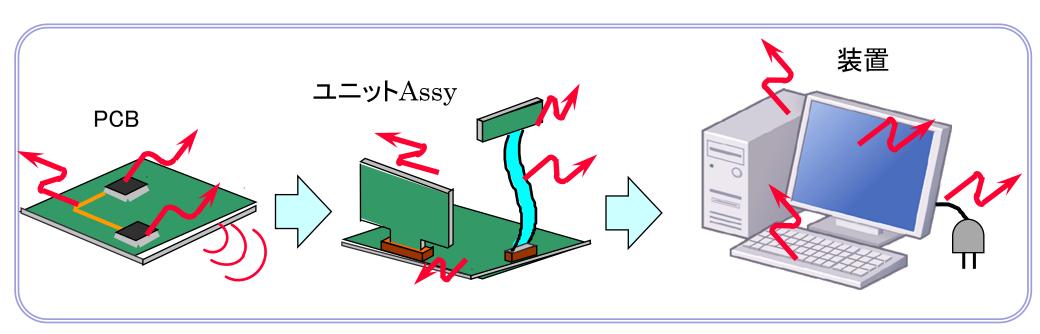

- ◆ シミュレーションの有効活用 レビューだけでは対応できない PCB、ユニットAssy、装置 への適用

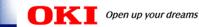

# 2.工程毎レビューの有効性

# 各ステップでのEMCに特化したレビューが重要

くく 他部門含めてのキーマンの参加が重要 >>

#### 2. 1 方式設計レビュー

方式設計

具体設計 • 製造設計

製造 • 評価

・回路設計機構設計場合によってはソフト設計のメンバとの意識合わせを行い 装置全体のEMC設計の大枠を確認する。

#### レビューでの確認項目例

- 1. 装置の電源・GND設計 ・・・・・・・・・・・・・・・・・・・ 事例1. 2

- 2. 筐体内の基板 や ハーネスのルートの検討・制約事項 ・・・・・ 事例3

- 3. 実施するシミュレーションの選定 ・・・・・・・・・・・・・・ 事例4

- 4. フレキケーブルの必要性の検討

- 5. 流用・参考基板の選定、 使ってよい部品・いけない部品の選定

- 6. 必要な試験プログラムの確認

- 7. その他

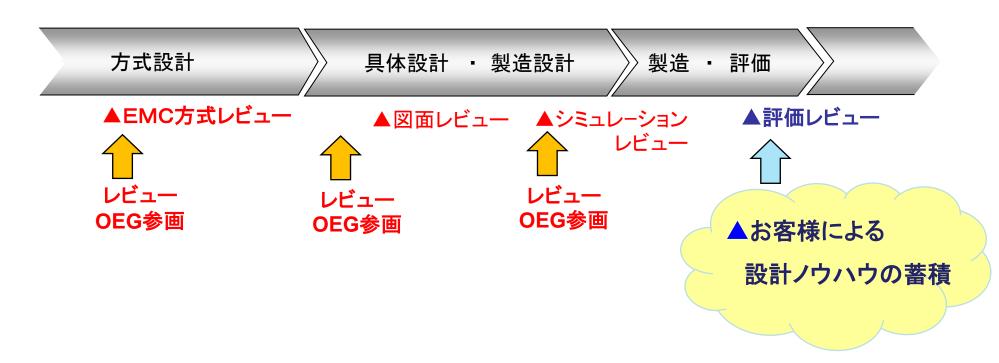

#### 方式設計事例1. GND(グランド)設計

#### 筐体GND(FG)と信号GND(SG)の考え方を装置内で統一する

- ①多点ショート

- ②1点ショート

- ③コンデンサショート

- 4)完全分離

装置仕様により確定する

#### 多点ショートの事例

大きな安定した一つのGNDを構築し磁束LOOP を起こさない様に、可能なかぎりの多点で SG-FGを金属ネジで接続する

SG座:基板上のシグナルグランド座

FG: フレームグラント (板金筐体)

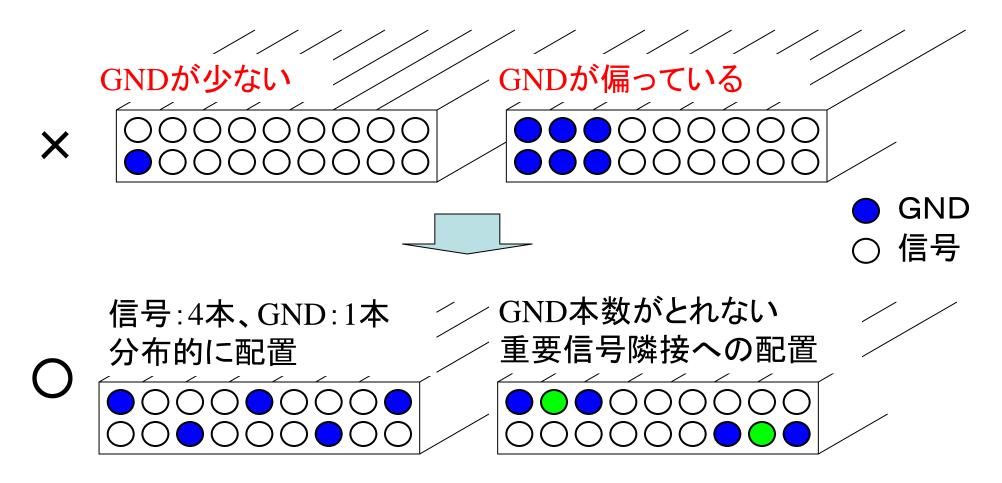

#### 方式設計事例2. GND設計

### インタフェースハーネス GNDピンの配置方法

■ GNDピン数とピン配列 理想は全芯数の半分をGNDにする

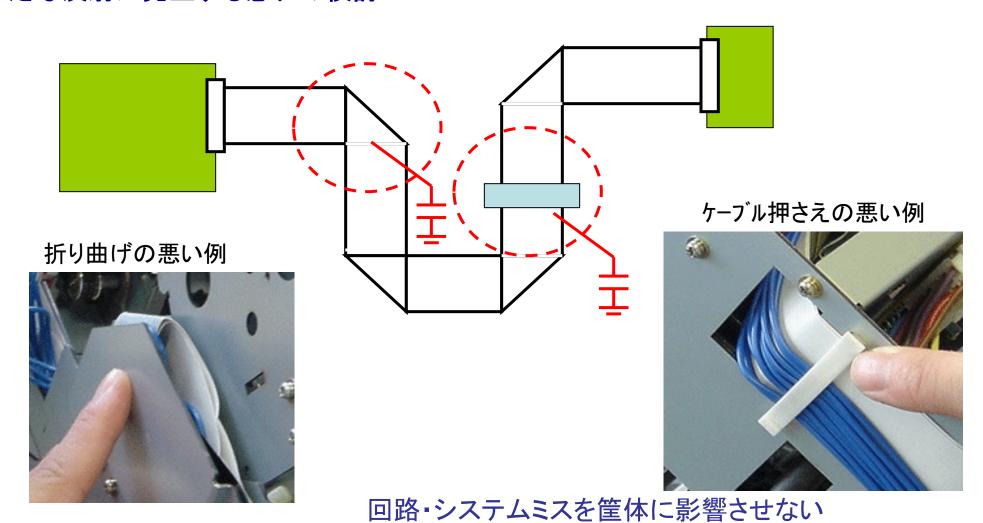

## 方式設計事例3. 筐体とハーネスとのC結合の回避

ハーネスのルート 折り曲げ、配線止め点でケーブルインピーダンスが変化している為 大きな反射が発生する恐れの検討

#### 方式設計事例4. 実施シミュレーションの一例

#### 適用するシミュレーションを選定する

- ①Signal Integrity (信号品質)

- ②Power Integrity (電源品質)

- ・ターゲットインピーダンス

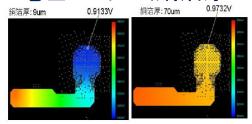

#### ・DC電圧ドロップ(銅箔厚と電圧降下)

引用資料:沖プリンテッドサーキット

## - 共振解析

#### アートワーク部門との 連携が重要

#### ・同時スイッチング対策

引用資料:沖プリンテッドサーキット

#### ・DC電流解析(電圧分布と電流ベクトルプロット)

引用資料:ANSYSカタロクブ

## 2. 2 具体設計レビュー

方式設計

具体設計 · 製造設計

製造 • 評価

#### ▲図面レビュー

具体設計時の回路図レビューでの確認項目例

1. バス線や重要信号線のトポロジー(形状)の確認

2. コンデンサの使い方の確認

3. GNDを弱くしない部品の使用法

4. 内層分割指示図と回路の確認

5. 表層ベタGNDと内層GNDの接続VIAの確認

6. その他

••• 事例1

••• 事例2

••• 事例3

••• 事例4

#### 注意

\*EMCレビューと回路(論理)レビューを同時に実施する場合 EMCレビューの意味合いが薄れてしまう恐れがある

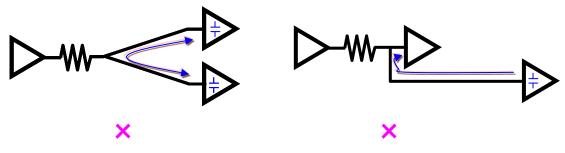

#### 具体設計事例1.トポロジー検証

# 部品の配置・配線時点で波形品質(SignalIntegrity)が決定するシミュレーションで確認する信号を見極めておく

●反射の影響を確認する 片方向 1対2

入力CとパターンのCが悪影響

●反射の影響を確認する 双方向バス 1対N

二つのレシーバを抵抗と配線で 同じインピーダンスに見せる

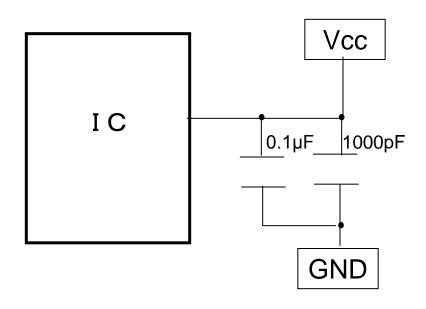

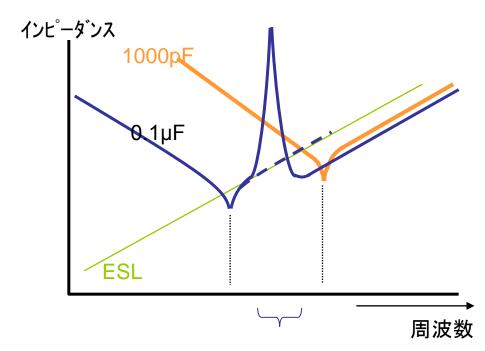

#### 具体設計事例2. 複数種コンデンサの実装例

#### セラミックコンデンサの周波数特性、半共振の発生を理解して配置が必要

特性、優先配置 等意味を理解 せずつけても効果なし

⇒明確な配置指示が必要

2種のコンデンサの合成されたものは、 半共振して高インピーダンス領域が 発生してしまう

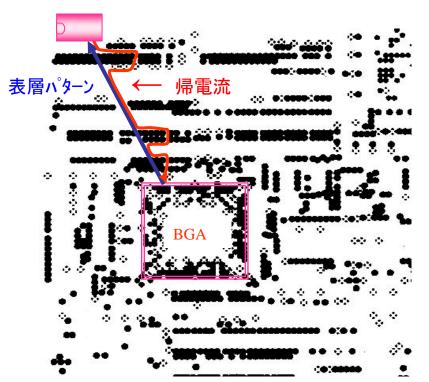

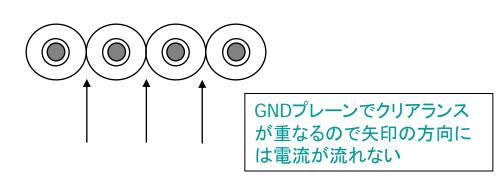

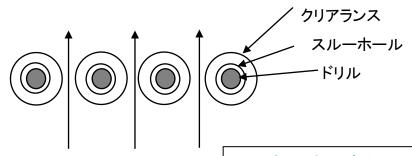

#### 具体設計事例3. GNDプレーンがVIA(孔)のクリアランスで弱くなる (GNE

(GND設計)

①LSI周辺のVIAのクリアランス、

抵抗VIAのクリアランスで 内層GNDが

孔だらけでベストな帰電流ルートが確保困難

### ②ピンヘッダの周囲も帰電流断となる。

同じドリル径でもクリアランス 径が小さくすれば動箔が残り 電流の流れるルートが確保で きる

製造設計部門への明確な指示を行う

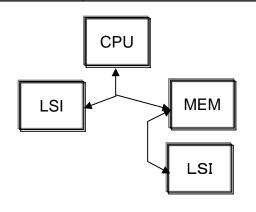

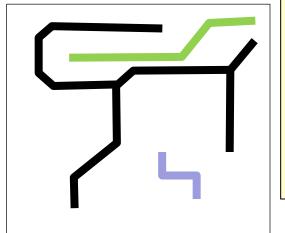

## 具体設計事例4. 内層設計ミスによるNG事例

L2(GND)

L3(VCC)

#### 問題点

- ・根拠なくGNDが分割されている

- ・VCCが大きくLOOPする線電源 配線となっている

対策後

対策前

#### 対策点

- ・大きな一つの安定したGND形成

- VCCのLOOP配線を削除した

#### 2. 3 シミュレーションレビュー

方式設計

具体設計 • 製造設計

製造 • 評価

・設計時の注意箇所の確認 完全にできなかったところ(妥協点)の確認

各種シミュレーションの活用

PCB シグナル インテグリティ

PCB パワー インテクリティ

装置·PCB 構造条件 シミュレーション結果が全てではないが、悪い結果には必ず要因が存在する

E M C

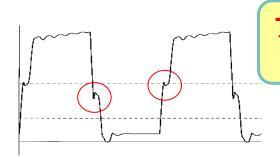

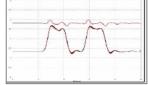

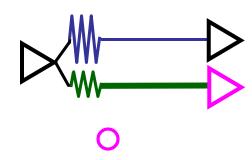

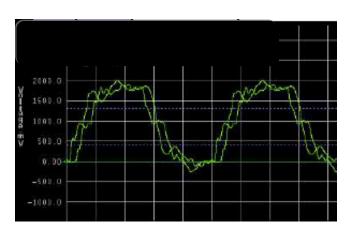

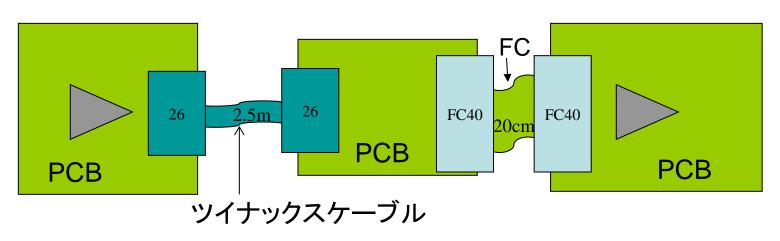

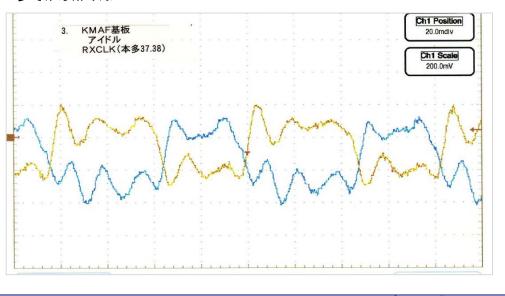

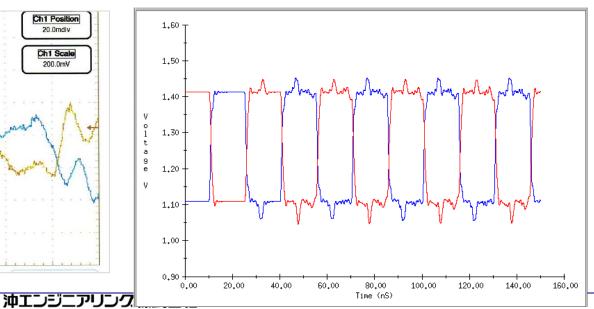

#### **シミュレーション事例1**. <u>350MbpsLVDS伝送 中継失敗事例</u>

#### 複数の基板とハーネスを結合させた波形シミュレーションで確認

#### 実測波形

## シミュレーション 等遅延配線実施

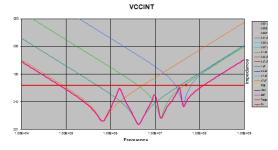

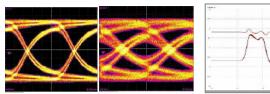

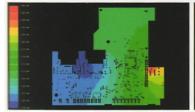

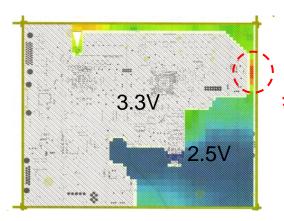

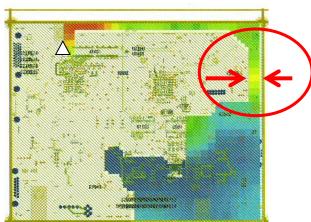

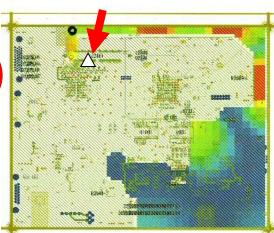

#### シミュレーション事例2. 電源プレーン共振

①コンデンサ1個追加 ××

#### ◆基板では、電源プレーンの形状、コンデンサの配置 状況、配置数から電源プレーン共振が発生します

例)

約30cm四方 の8層基板の VCC層

赤: 共振してる ノイズ源

# ②右側のラインを太く ×

ででで 電源 バウンス GND GNDバウンス

③ ②+パスコン1個追加 ××

沖エンジニアリング株式会社

## 2.4 評価レビュー

#### ▲評価レビュー

・評価で確認した内容に加えて、今回の設計で効果のあった施策、なかった施策を まとめて次につなげるナレッジデータベースを構築することが重要と考えます。

#### 構築手段例

- •CADシステムに組込み

- •イントラネット上で情報共有

- チェックリスト作成

- ・その他

#### 評価レビュー 事例. チェックリストの活用

#### 個別の設計段階ではレビューの代わりにチェックリストでも確認できる

#### 回路図チェック表

| PJ名称    | 設計 |  |

|---------|----|--|

| チェック日   | 険図 |  |

| 基板名称/図番 | 承認 |  |

内容は日々更新し、 陳腐化した内容は 削除していく

チェック欄記入方法 ○:確認、△:条件付きOK、/:該当しない

| ナエツ | ク欄記入方法 〇:帷認、△:余件付ぎOK、/:該当しない                  |      |

|-----|-----------------------------------------------|------|

| No. | 項目                                            | チェック |

| 1   | 接続チェック、論理チェック、極性チェックは行ったか。                    |      |

|     | (流用元回路図を参照しながら。)                              |      |

| 5   | ハードウェア仕様書(命令説資)と回路図の照合をしたか。                   |      |

| 6   | コネクタ、IC、各シンボル等のピン番を確認したか。(DIP、SOPでピン番が違う)     |      |

|     | ICの形状チェック(SOJ、ZIP、DIP、etc)は行ったか。              |      |

| 7   | 空き入力端子を確認したか。(CMOS:OVに落とす or 低消費電流側)          |      |

| 8   | 使用素子はドライブ能力が大きすぎないか。早過ぎないか。(FPGAバッファコントロール、等) |      |

| 9   | コンデンサの容量、耐圧、数量を確認したか。アナログ電源にも入っているか。          |      |

|     | (積層セラミックは耐圧2.5倍以上必要、アナログ電源は3倍以上、難しい場合は        |      |

|     | 小形・大容量に拘らず、クラック防止を考慮する。電解コンは定格の 80%以内)        |      |

| 1 0 | 0.1μF以外のパスコンの配置は効果を把握しているか?基本は禁止。             |      |

| 1 1 | コネクタピン番チェック(図面と照合)したか。                        |      |

| 1 3 | 回路図の部分コピーを行った所は、塗りつぶしチェックをしたか。                |      |

|     | 同じ容量のC、Rが2図番(特性、サイズ 違い等)で使用されてないか。            |      |

|     |                                               |      |

- ・パターン図

- •部品配置

- •組立実装図

- ・ハーネス

- 板金

- •その他

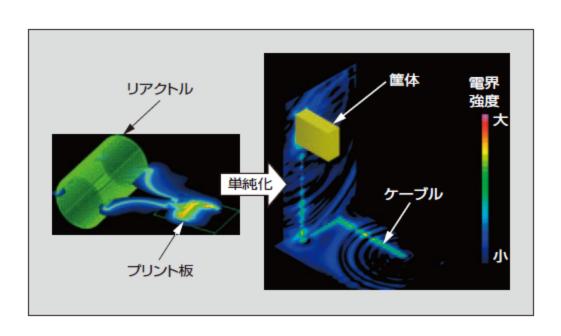

# 3. 電源デバイスのEMC留意事項

- ■DC/DCコンバータ 3端子レギュレータ の選定 小型装置ではエネルギーの拡散に留意 部品コストだけで選定する失敗事例あり

- ■大型デバイスでは、専用フィルタのシミュレーションも有効 課題 モデリングの複雑さからの製品適用が困難

ノイズ発生デバイス だがPCB上に配置 され影響を与える

引用資料 富士電機㈱ 富士時報 Vol.84 No.2 2011

# 4. まとめ

製品開発プロセスにおいて、出荷間際のEMC評価で問題を起こさない為に、

フロントローディング手法として EMC設計を実践することが重要です。

EMC設計を実践しておくこと、つまり有意義なレビュー、必要なシミュレーションを実施

することで、仮に課題が発生したとしても、「真の問題点を解決する」 為の時間・コスト

は大幅に短縮できると考えてます。

OKIエンジニアリングでは、EMC対策で設計段階に後戻りすることなく、市場に製品をタイムリーに提供できる様に EMC設計 にご協力いたします。

## ご清聴いただき、ありがとうございました

》お問合せ先

#### 沖エンジニアリング、株式会社

□ EMC事業部 車載グループ

□ 担当:戸所祐策

□ お問合せフォーム: https://www.oki.com/cgi-bin/inquiryForm.cgi?p=k039

□ URL: http://www.oeg.co.jp/

Open up your dreams