#### 2008 OEGセミナー

## 車載電子部品における ESD・ラッチアップ試験の現状と実績

2008年7月8日

沖エンジニアリング株式会社

信頼性設計事業部 加藤 且宏

## 目次

- 1. 車載電子部品におけるESD・ ラッチアップ試験の現状と課題

- 2. 評価 · 解析事例

- 3.各試験への沖エンジニアリングの適応状況

- 4. まとめ

# 車載電子部品における ESD・ラッチアップ試験の 現状と課題

#### 自動車のエレクトロニクス化の加速

従来:制御系システム(主にマイコン) 現在~将来:無線・画像・パワー系など多様化

エンジン・コントロール・ユニット パワー・ウィンドウ オートマチック・トランスミッション パワー・ステアリング アンチロック・ブレーキシステム エアバッグ・システム 各種センサ・RF無線通信 インテリジェントパネル(カーナビからPCへ) インバータ(電力制御) 路車間通信(オートクルーズ)

自動車の電子化がキーテクノロジ

利便性

省エネ性

静電破壊耐性・ラッチアップ耐性

→部品レベルでの信頼性の作り込み

URL: http://www.oeg.co.jp/

快適性

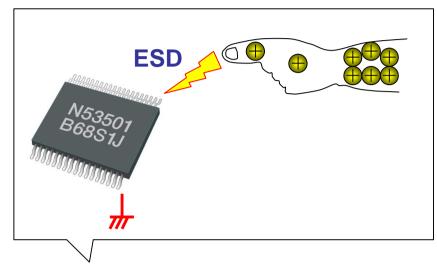

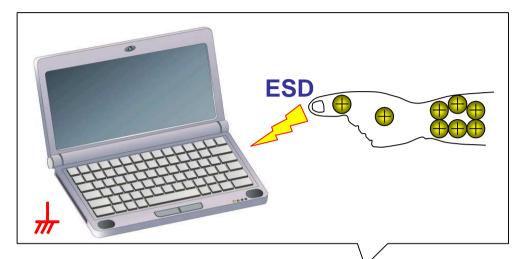

#### 静電破壊とラッチアップ

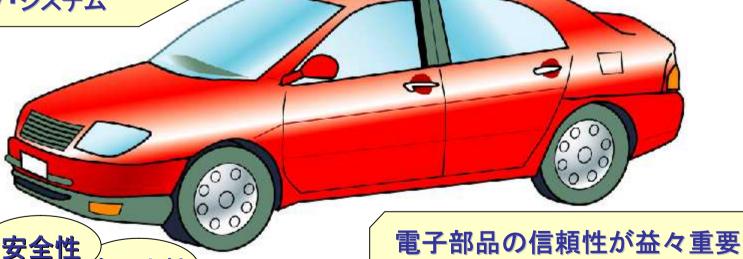

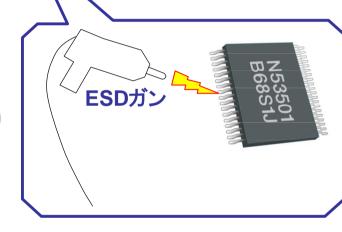

静電破壊(ESD: Electro-Static Discharge) 静電気放電によってデバイスが破壊される現象。

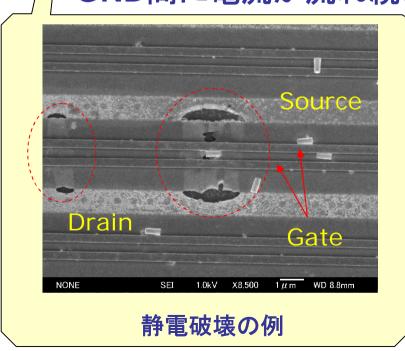

ラッチアップ (Latch-up)

CMOSデバイスの寄生サイリスタがターンオンし、電源ーGND間に電流が流れ続ける現象(デバイス破壊発生)

#### 静電破壊・ラッチアップ耐性の試験方法

- ・電子部品製造者が実施(半導体・ディスクリート)

- デバイス単体の破壊(劣化) 耐性評価

- ・ESD試験とラッチアップ試験が それぞれ存在

#### システムレベル試験

- ・システム製造者が実施 (電子部品ユーザ)

- ・システムの破壊(誤動作) 耐性評価

- ・破壊耐性がESD試験、 誤動作耐性がラッチアップ試験

## ESD試験の現状と課題

#### 同一名称で異なる試験規格

|                   | コンポーネント(部品)ESD試験 |                 |                |              |               | システムESD試験         |               |

|-------------------|------------------|-----------------|----------------|--------------|---------------|-------------------|---------------|

| 規格名種類             | JEITA<br>ED-4701 | JEDEC<br>JESD22 | ESDA<br>STM5.X | AEC-<br>Q100 | IEC-<br>60749 | IEC-<br>61000-4-2 | ISO-<br>10605 |

| HBM               |                  |                 |                |              |               |                   |               |

| MM                | -                |                 |                |              |               | -                 | -             |

| <b>Direct-CDM</b> |                  | -               |                |              |               | -                 | -             |

| FI-CDM            | -                |                 |                |              |               | -                 | -             |

- ・部品ESD試験/システムESD試験 ともにHBM (Human Body Model)

- ・試験回路、強度分類が異なる

#### 部品(デバイス)メーカの動向と環境変化

システムレベルESD試験規格への適合性をアピールする動き

(M社、N社ともに有力なAECメンバー)

·システムの小型·軽量化 (ESDストレスの影響:大)

システムESD試験のストレスが部品単体へ 加わりやすいアプリケーション (アンテナ端子、インターフェイス機器接続端子)

システムESD試験がデバイス単体の信頼性でも差別化の要素になりつつある

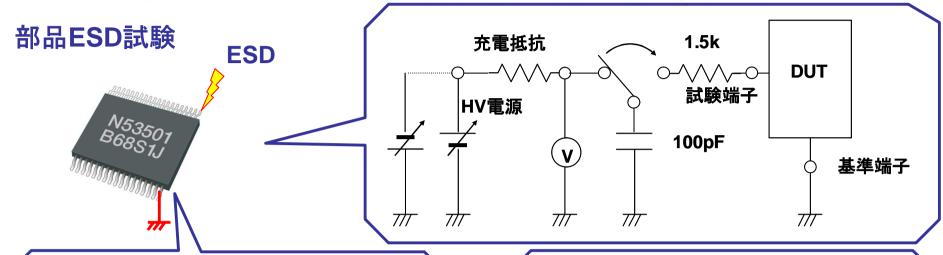

#### 部品ESD試験の放電回路と強度区分

#### AEC-Q100 002 RevDの 強度区分

| НО  | 0~250 <b>V</b>     |  |  |  |

|-----|--------------------|--|--|--|

| H1A | 251~ <u>500V</u>   |  |  |  |

| H1B | 501~ <u>1000V</u>  |  |  |  |

| H1C | 1001~ <u>1500V</u> |  |  |  |

|     | 1501~ <u>2000V</u> |  |  |  |

| H2  | 2001~4000V         |  |  |  |

| НЗА | 4001~8000 <b>V</b> |  |  |  |

| нзв | 8001 <b>V</b> 以上   |  |  |  |

要求耐性>2kV (Ipeak: 1.33A)

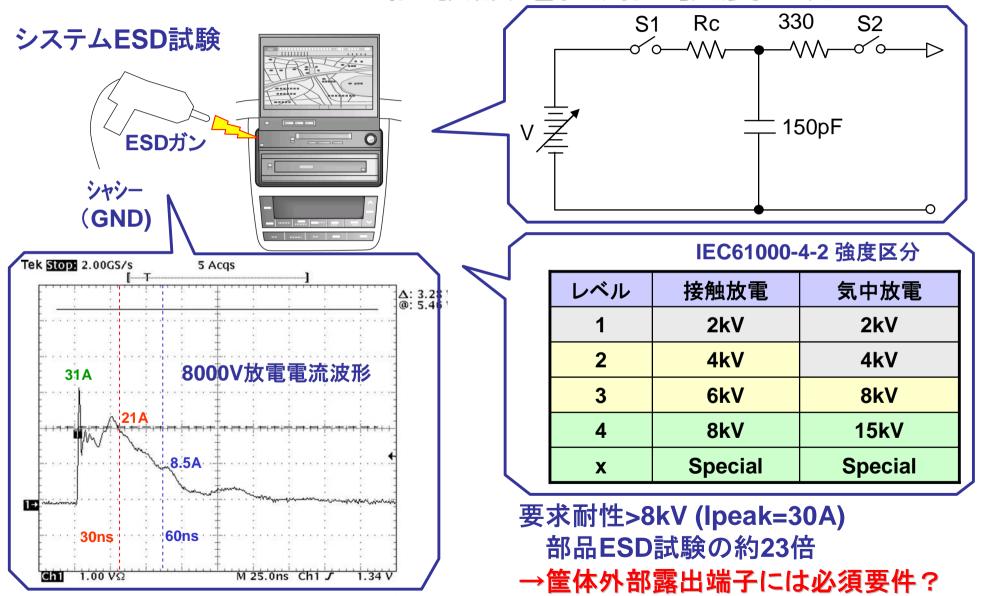

#### システムESD試験放電回路と強度区分

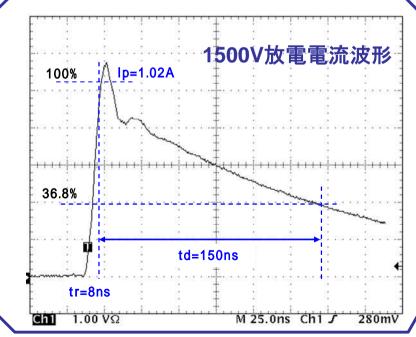

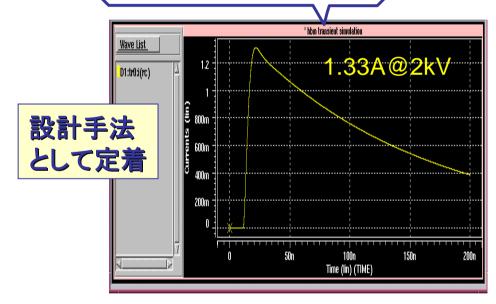

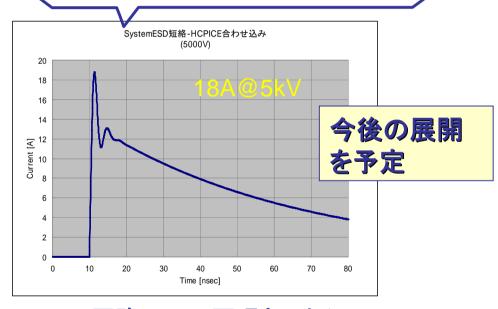

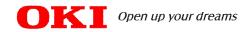

#### システムESD対応設計への SPICEシミュレーションの応用

電子部品の保護回路をSPICE シミュレーションを使って最適化する手法

部品ESD試験対応保護 回路設計では一般化

SPICE回路Sim.で再現させた部品 ESD試験放電電流波形

システムESD試験対応保護回路 設計にも適用可能

SPICE回路Sim.で再現させたシステムESD試験放電電流波形

システムESD試験の放電ストレスにもSPICE\_Simを適用できる環境が整いつつある

#### SPICEシミュレーション適用に向けた課題

- ・システムESD試験=「閉じていない回路」

- ・印加側と接地側の容量と抵抗の見積

- ・サージの畳重効果の有無(反射波の影響)

- ・放電波形の測定(GHz帯インパルス波形の計測)

URL: http://www.oeg.co.jp/

**VDD**

## ラッチアップ試験の現状と課題

#### ラッチアップ試験の課題~トリガパルスの乖離

|       | コンポーネント(部品)ラッチアップ試験 |        |        |      |       | システムイミュニティ試験 |       |

|-------|---------------------|--------|--------|------|-------|--------------|-------|

| 規格名   | JEITA               | JEDEC  | ESDA   | AEC- | IEC-  | IEC-         | ISO-  |

| 種類    | ED-4701             | JESD78 | STM5.X | Q100 | 60749 | 61000-4-2    | 10605 |

| 電流パルス |                     |        | -      |      |       | -            | -     |

| 電圧パルス | -                   | -      | -      | -    | -     |              |       |

| 電源過電圧 |                     |        | -      |      | _     | -            | -     |

- ・システム誤動作試験は電圧ノイズ

- ・トリガ源が両者で異なる

- ・部品ラッチアップ試験に電圧パルスの公的規格は存在しない

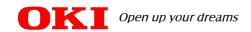

部品ラッチアップ試験回路と強度区分

#### 要求耐性>100mA (Ta; Max) トリガパルス幅: 5usec~5sec

M2.00ms Ch1 J

50%

50%

M 200us Chi (100 V

10msec

tp=10ms

$V_{D} = 10.0V$

tr=300us

10%

Chi 2.00 V

Tek Stop: 2.00GS/s

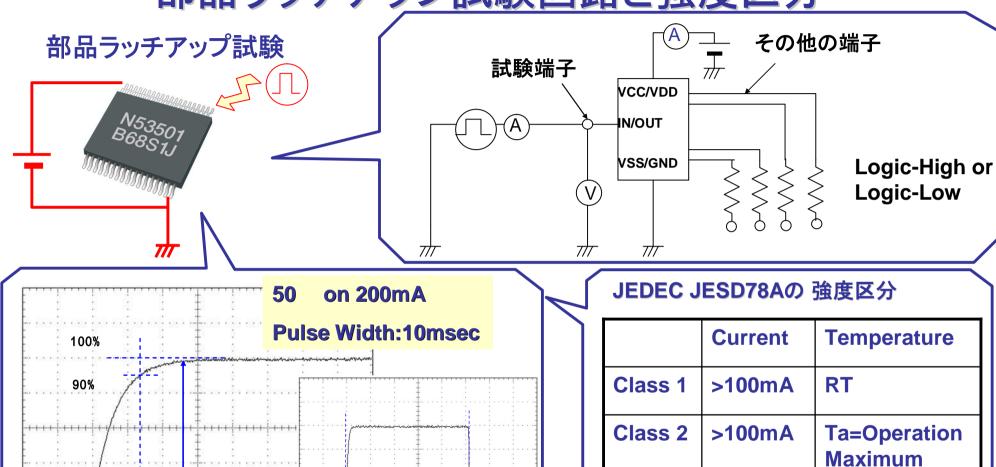

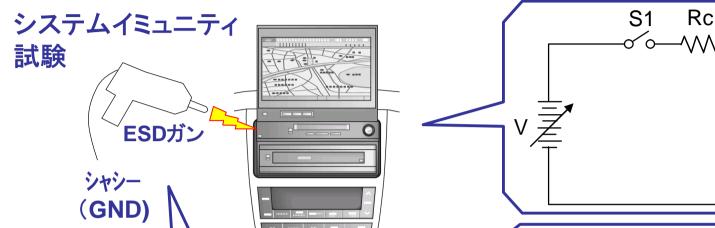

#### システムイミュニティ試験放電回路と強度区分

Δ: 3.28 @: 5.46

#### IEC61000-4-2 強度区分

| レベル | 接触放電    | 気中放電    |

|-----|---------|---------|

| 1   | 2kV     | 2kV     |

| 2   | 4kV     | 4kV     |

| 3   | 6kV     | 8kV     |

| 4   | 8kV     | 15kV    |

| X   | Special | Special |

31A 8000V放電電流波形 21A 8.5A 30ns 60ns

M 25.0ns Ch1 J

5 Acqs

要求耐性>8kV (Ipeak=30A) トリガパルス幅: ~数100nsec

(トランジェント電圧パルス)

1.00 VΩ

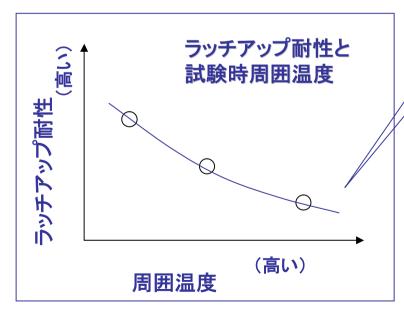

#### ラッチアップ試験の課題~温特評価の必要性

|       | コンポーネント(部品)ラッチアップ試験 |                |        |      |       | システムイミュニティ試験 |       |

|-------|---------------------|----------------|--------|------|-------|--------------|-------|

| 規格名   | JEITA               | JEDEC          | ESDA   | AEC- | IEC-  | IEC-         | ISO-  |

| 種類    | ED-4701             | JESD78         | STM5.X | Q100 | 60749 | 61000-4-2    | 10605 |

| 電流パルス |                     |                | -      |      |       | -            | 1     |

| 電圧パルス | ı                   | 1              | -      | -    | -     |              |       |

| 電源過電圧 |                     |                | -      |      |       | -            | •     |

| 周囲温度  | R                   | RT 又は 最大動作保証温度 |        |      |       | RTのみ         |       |

#### ラッチアップ耐性は高温で低下

部品ラッチアップ 試験は最大動作 保証温度で実施

システムイミュニティ 試験は室温で実施 (高温下で実施困難)

部品単体の電圧パルス・ラッチアップ試験 最大動作保証温度で実施

システムイミュニティ試験補完の可能性

#### 部品試験とシステム試験の課題と方策(まとめ)

#### ESD試験

- 部品ESD試験とシステムESD試験ともにHBM

- ・部品単体にシステムESD試験耐性を求める流れ

- ・システムの小型化(サージ吸収能力の低下)

- ・部品端子がサージに晒されやすいアプリケーション

- ·Sim手法による最適化(必要な端子に適切な保護回路)

#### ラッチアップ試験

- ・部品ラッチアップ試験とシステムイミュニティ試験での トリガパルスの乖離

- ・部品ラッチアップ試験への電圧パルス試験の取り込み →(トランジェントラッチアップ)規格化

- ・部品ラッチアップ試験によるイミュニティ試験高温保証の代替

## 2. 適用事例のご紹介

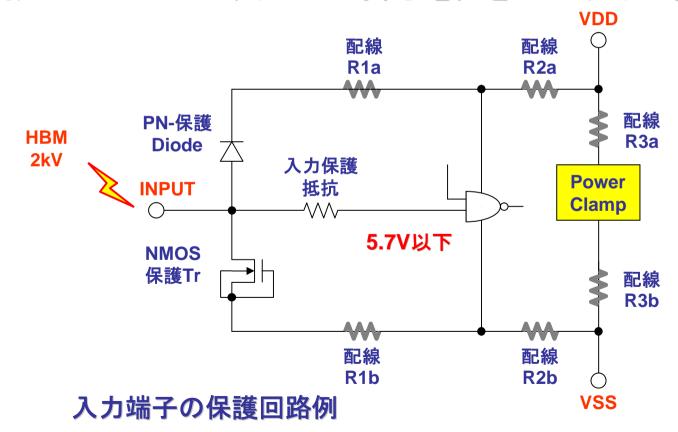

## SPICEシミュレーションを 用いた保護回路設計例

#### ESDシミュレーションによる保護回路設計

ESDサージを印加した時、所定のノードの電位が設定値を超えないように保護回路を構成する手法

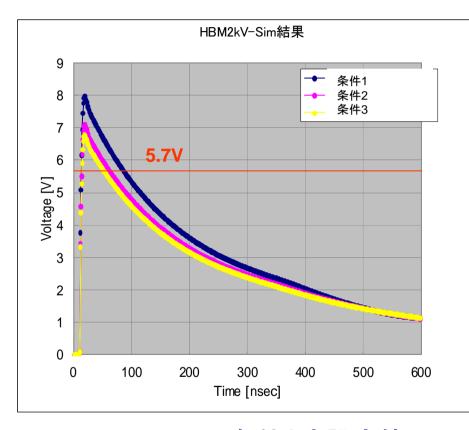

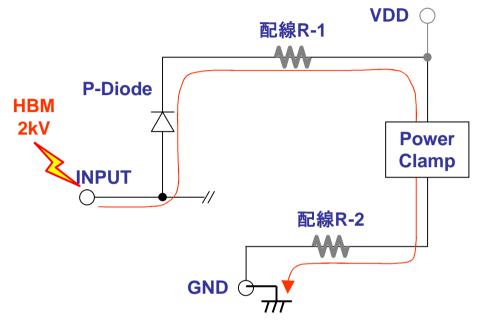

(例) HBM:2kVで、ゲートに掛る電位を5.7V以下に抑える

#### ESDシミュレーション結果(回路構成)

#### 【PMOS保護の場合】

#### 【Diode保護の場合】

HBM2kV-Sim結果 9 条件1 条件2 8 条件3 7 5.7V 6 Voltage [V] 3 2 1 0 100 200 300 400 500 600 Time [nsec]

PMOSでは、3条件とも設定値 をオーバー 不適

ダイオードでは、条件1のみ設定値を オーバー 条件2を採用

#### ESDシミュレーション結果(配線抵抗)

0.6 まで許容範囲→バラツキを考慮して0.5 以下

(配線R-1)+(配線R-2) 0.5

| 配線R   | INPUT電位 | 判定   |  |

|-------|---------|------|--|

| [ohm] | [V]     | 刊人   |  |

| 0     | 4.85    | Pass |  |

| 0.1   | 4.98    | Pass |  |

| 0.2   | 5.11    | Pass |  |

| 0.3   | 5.25    | Pass |  |

| 0.4   | 5.38    | Pass |  |

| 0.5   | 5.51    | Pass |  |

| 0.6   | 5.65    | Pass |  |

| 0.7   | 5.78    | Fail |  |

| 0.8   | 5.91    | Fail |  |

| 0.9   | 6.04    | Fail |  |

| 1     | 6.18    | Fail |  |

#### SPICEシミュレーションを用いた保護回路設計(まとめ)

- ・半導体デバイスの保護回路設計に用いられる手法

- ・SPICEパラメータを使って、ESDサージが入った時の 所定ノードの過渡電圧をシミュレーションする手法

- ・本手法を使うことで、保護回路面積を最適化する (ESD耐性対コスト)

- ・この種の手法をシステムレベルESD試験の保護回路設計に応用することで、同様の効果を期待できる

## 故障解析と対策例

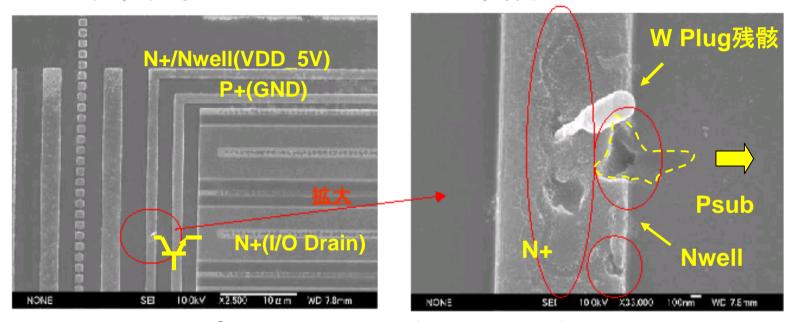

#### ガードリングの破壊

#### Coサリサイドプロセス / NMOS出力Tr

VDD5VをコモンにI/Oポートへ(ー)サージを印加した時に発生症状はサージを印加したI/O端子自身のリークではなく、5V\_IDD不良ドレインのN+に向かってサージ電流が流れた痕跡寄生npnTr='ガードリング(N+)ー基板(P+)ーI/Oのドレイン(N+)'のコレクタ側接合が破壊(ドレイン=I/O端子側は順方向なので破壊しない)

#### 故障解析と対策(まとめ)

- -ESD試験で発生した故障品の解析事例

- ・破壊の痕跡と寄生バイポーラTrの構造から 故障メカニズムを想定

- ・サリサイド構造Trの脆弱性(サージの局所集中)

- ・ベース・フローティング状態での寄生バイポーラの挙動

- ・素子面積の増加を抑えた改良方法を検討

## 3.沖エンジニアリングにおける 各種試験への適応状況

#### 各種試験規格への適応状況

|                   | コンポーネント(部品)ESD試験 |        |        |      |       | システムESD試験 |       |

|-------------------|------------------|--------|--------|------|-------|-----------|-------|

| 規格名               | JEITA            | JEDEC  | IEC-   | ISO- |       |           |       |

| 種類                | ED-4701          | JESD22 | STM5.X | Q100 | 60749 | 61000-4-2 | 10605 |

| HBM               |                  |        |        |      |       | ***       | ***   |

| MM                | -                |        |        |      |       | -         | -     |

| <b>Direct-CDM</b> |                  | 1      |        |      |       | -         | -     |

| FI-CDM            | -                | *      | *      | *    | *     | -         | -     |

|       | コンポーネント(部品)ラッチアップ試験 |        |        |      |       | システムイミュニティ試験 |       |

|-------|---------------------|--------|--------|------|-------|--------------|-------|

| 規格名   | JEITA               | JEDEC  | ESDA   | AEC- | IEC-  | IEC-         | ISO-  |

| 種類    | ED-4701             | JESD78 | STM5.X | Q100 | 60749 | 61000-4-2    | 10605 |

| 電流パルス |                     |        | -      |      |       | -            | -     |

| 電圧パルス | **                  | -      | -      | -    | -     | ***          | ***   |

| 電源過電圧 |                     |        | -      |      |       | -            | -     |

<sup>\* 2008.7</sup>より、HED-C5002導入開始

<sup>\*\*</sup> 旧EIAJ AB6201 半導体信頼性委員会内部資料に準ずる \*\*\* 簡易評価

#### まとめ

- ・車載電子部品のESD/ラッチアップ試験のあらゆる ニーズに対応可能(受託試験から対策コンサルまで)

- ・SPICE\_SimのシステムレベルESD試験への適用 (納得性のあるソリューションをご提供)

- ・高温ラッチアップ試験の適用 (車載部品のノイズ誤動作耐性を ラッチアップ耐性の尺度でご提供)

- ・部品単体からシステム評価まで、どのような試験のご相談にも対応

## ご静聴、有り難う御座いました。

お問合せ先

#### 沖エンジニアリング、株式会社

信頼性設計事業部

TEL: 042-662-6778

福田保裕

E-mail: oeg-esdsales@oki.com

URL: http://www.oeg.co.jp/

ご連絡をお待ちしております

## (参考)規格制定団体の略称

JEITA: Japan Electronics and Information Technology Industries Association JEDEC: Joint Electron Device Engineering Council

**ESDA: ESD Association**

**AEC: Automotive Electronics Council**

**IEC: International Electrotechnical Commission**

**ISO:** the International Organization

for Standardization